This is an old revision of the document!

Network interface

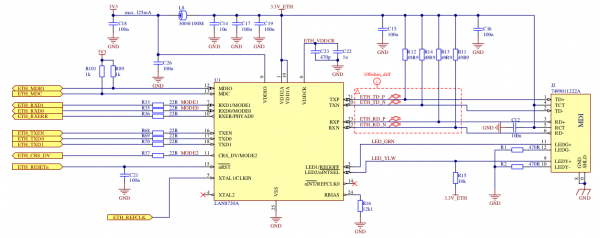

i.MX6UL contains Dual-Megabit Ethernet Controller. Below you can see how this peripheral is configured for the liteboard.

LAN8720A

|

Liteboard is using external LAN8720A 10BASE-T/100BASE-TX transceiver connected with liteSOM via RMII™ interface. Following signals are required to connect liteSOM with LAN8720A via RMII™:

In addition LAN8720A and liteSOM are connected via SMI signals:

|

Device Tree configuration

fec1: ethernet@02188000 {

compatible = "fsl,imx6ul-fec", "fsl,imx6q-fec";

reg = <0x02188000 0x4000>;

interrupts = <GIC_SPI 118 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 119 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clks IMX6UL_CLK_ENET>,

<&clks IMX6UL_CLK_ENET_AHB>,

<&clks IMX6UL_CLK_ENET_PTP>,

<&clks IMX6UL_CLK_ENET_REF>,

<&clks IMX6UL_CLK_ENET_REF>;

clock-names = "ipg", "ahb", "ptp",

"enet_clk_ref", "enet_out";

fsl,num-tx-queues=<1>;

fsl,num-rx-queues=<1>;

status = "disabled";

};

|

Basic configuration for Documentation for this device-tree node you can find in fsl-fec.txt file. |

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet1>;

phy-mode = "rmii";

phy-handle = <ðphy0>;

status = "okay";

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@0 {

reg = <0>;

};

};

};

&iomuxc {

pinctrl_enet1: enet1grp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO07__ENET1_MDC 0x1b0b0

MX6UL_PAD_GPIO1_IO06__ENET1_MDIO 0x1b0b0

MX6UL_PAD_ENET1_RX_EN__ENET1_RX_EN 0x1b0b0

MX6UL_PAD_ENET1_RX_ER__ENET1_RX_ER 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA0__ENET1_RDATA00 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA1__ENET1_RDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_EN__ENET1_TX_EN 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA0__ENET1_TDATA00 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA1__ENET1_TDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_CLK__ENET1_REF_CLK1 0x4001b031

>;

};

};

|

To enable -> Device Drivers

-> Network device support

-> Ethernet driver support

-> Freescale device

-> FEC ethernet controller (of ColdFire and some i.MX CPUs)

|